#### **General Description**

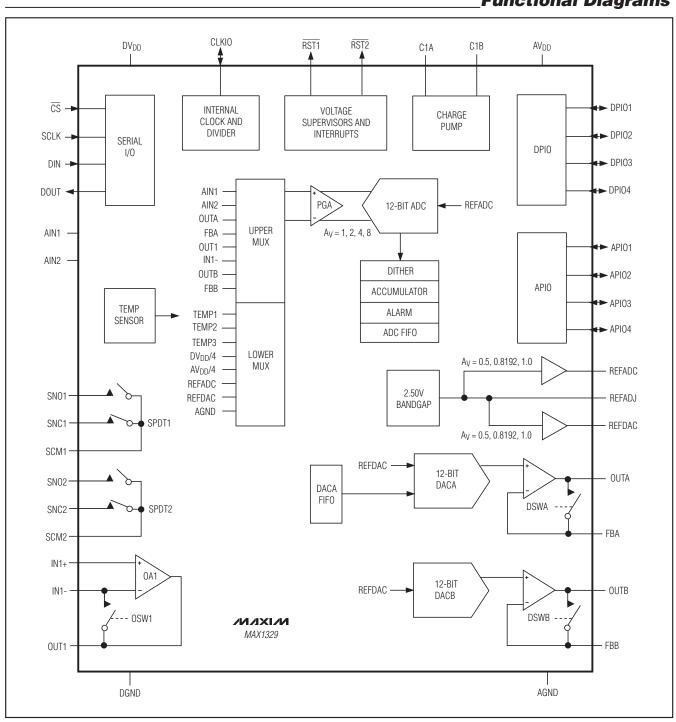

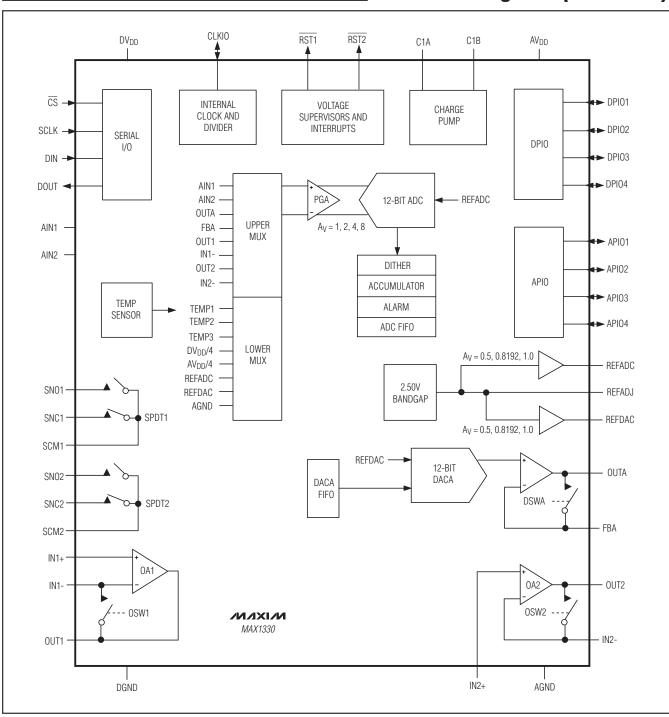

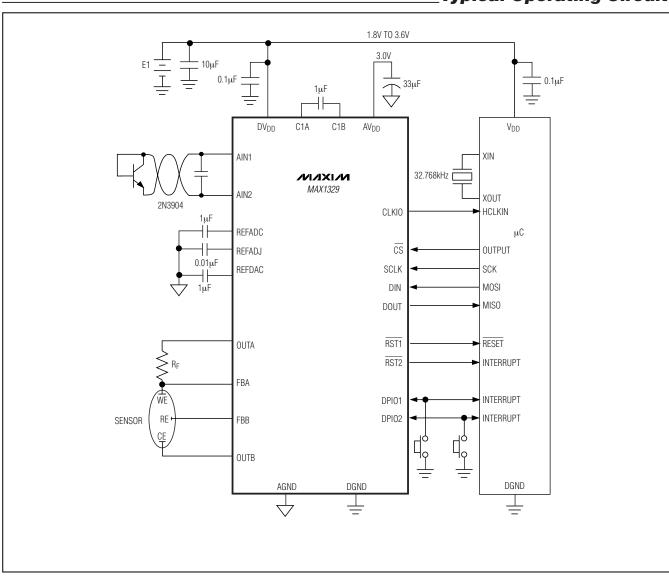

The MAX1329/MAX1330 are smart data acquisition systems (DASs) based on a successive approximation register (SAR) analog-to-digital converter (ADC). These devices are highly integrated, offering an ADC, digitalto-analog converters (DACs), operational amplifiers (op amps), voltage reference, temperature sensors, and analog switches in the same device.

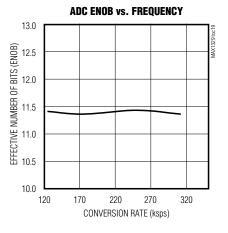

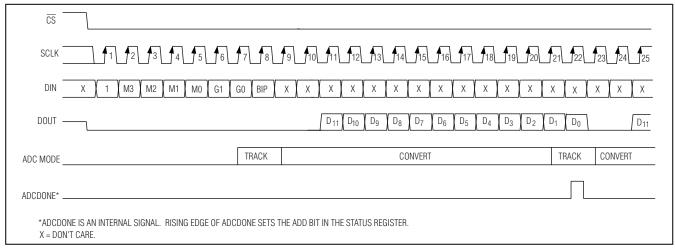

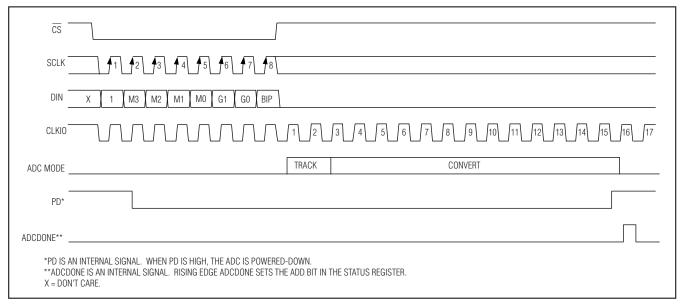

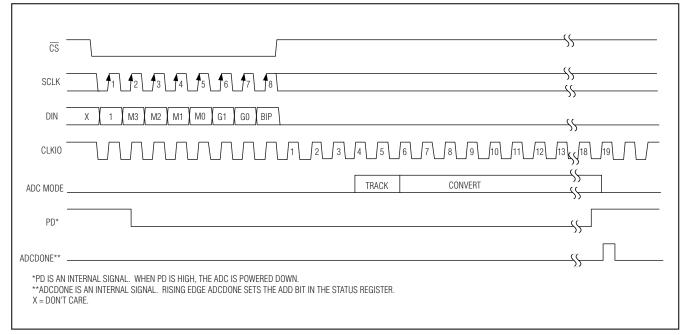

The MAX1329/MAX1330 offer a single ADC with a reference buffer. The ADC is capable of operating in one of two user-programmable modes. In normal mode, the ADC provides up to 12 bits of resolution at 312ksps. In DSP mode, the ADC provides up to 16 bits of resolution at 1000sps. The ADC accepts one external differential input or two external single-ended inputs as well as inputs from other circuitry on-board. An on-chip programmable gain amplifier (PGA) follows the analog inputs, reducing external circuitry requirements. The PGA gain is adjustable from 1V/V to 8V/V

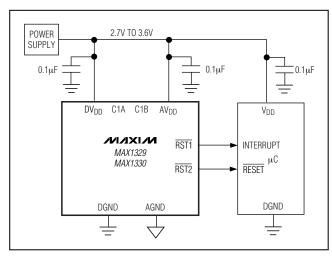

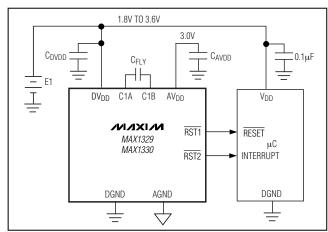

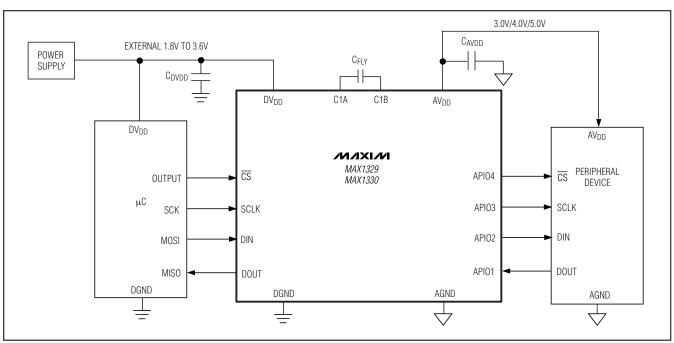

The MAX1329/MAX1330 operate from a 1.8V to 3.6V digital power supply. Shutdown and sleep modes are available for power-saving applications. Under normal operation, an internal charge pump boosts the supply voltage for the analog circuitry when the supply is < 2.7V.

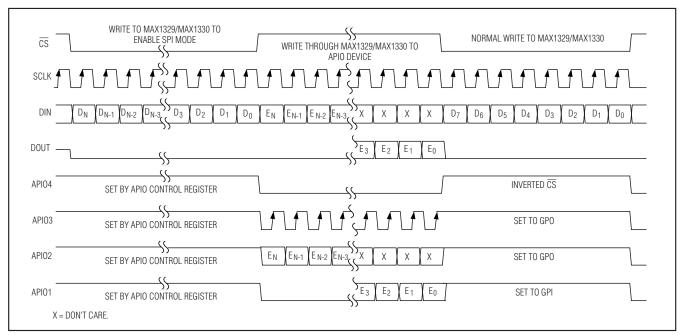

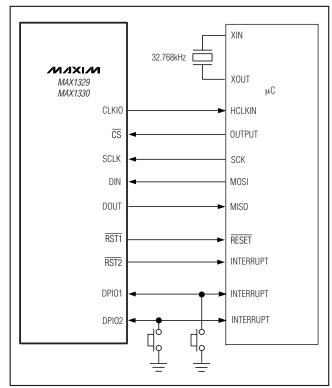

The MAX1329/MAX1330 offer four analog programmable I/Os (APIOs) and four digital programmable I/Os (DPIOs). The APIOs can be configured as general-purpose logic inputs and outputs, as a wake-up function, or as a buffer and level shifter for the serial interface to communicate with slave devices powered by the analog supply, AVDD. The DPIOs can be configured as generalpurpose logic inputs and outputs as well as inputs to directly control the ADC conversion rate, the analog switches, the loading of the DACs, wake-up, sleep, and shutdown modes, and as an interrupt for when the analog-to-digital conversion is complete.

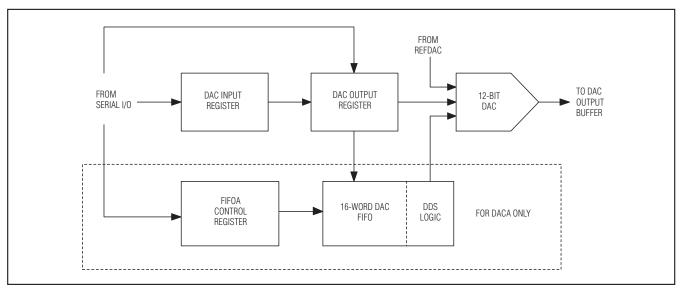

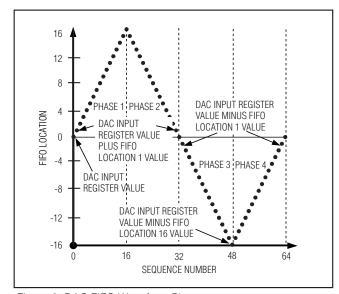

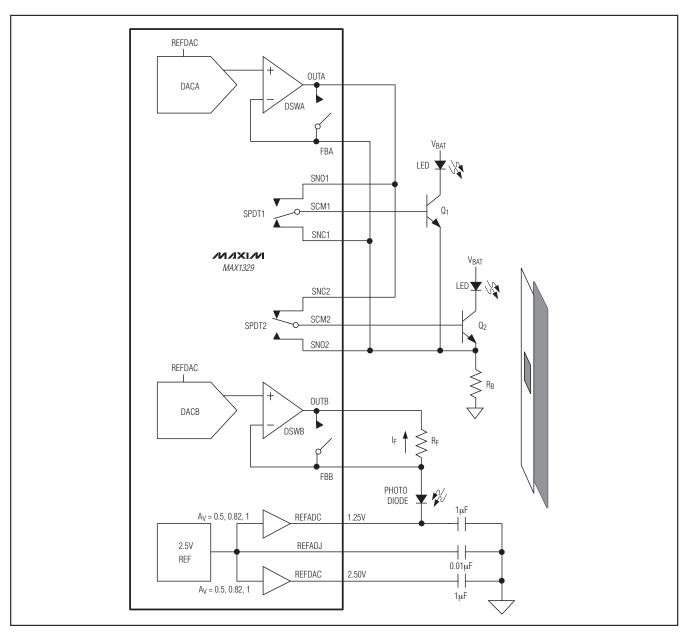

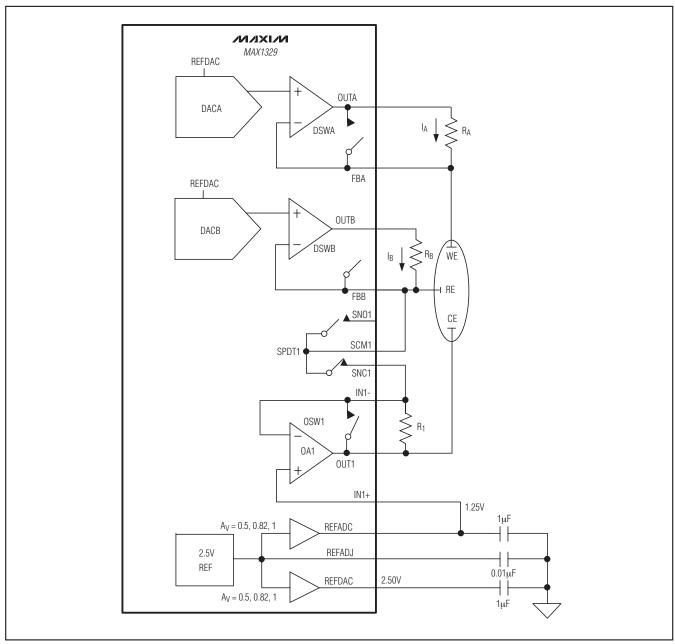

The MAX1329 includes dual 12-bit force-sense DACs with a programmable reference buffer and one op amp. The MAX1330 provides one 12-bit force-sense DAC with a programmable reference buffer and two op amps. For the MAX1329/MAX1330, a 16-word DAC FIFO can be used with the DACA for direct digital synthesis (DDS)

The 4-wire serial interface is compatible with SPI™, QSPI™, and MICROWIRE™.

### **Applications**

Battery-Powered and Portable Devices Electrochemical and Optical Sensors Medical Instruments Industrial Control **Data Acquisition Systems** Low-Cost CODECs

SPI/QSPI are trademarks of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp. **Features**

- ♦ 1.8V to 3.6V Single Digital Supply Operation

- ♦ Internal Charge Pump for Analog Circuits (2.7V to 5.5V)

- ♦ 12-Bit SAR ADC

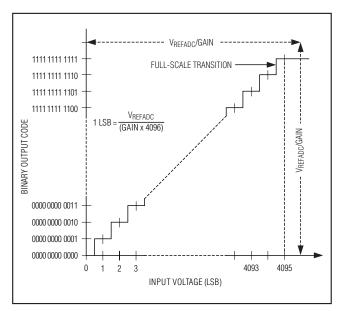

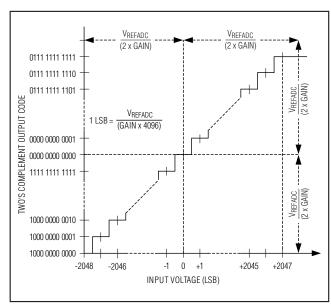

12 Bits, 312ksps, No Missing Codes 16 Bits, 1000sps, DSP Mode 16-Word FIFO and 20-Bit Accumulator PGA with Gains of 1, 2, 4, and 8 **Unipolar and Bipolar Modes 16-Input Differential Multiplexer**

- ♦ Dual 12-Bit Force-Sense DACs 16-Word FIFO (DACA Only)

- Independent Voltage References for ADC and DACs Internal 2.5V Reference Adjustable Reference Buffers Provide 1.25V, 2.048V, or 2.5V

- ♦ System Support **ADC Alarm Register Uncommitted Op Amps Dual SPDT Analog Switches** Internal/External Temperature Sensor Internal Oscillator with Clock I/O Digital Programmable I/O Analog Programmable I/O **Programmable Interrupts Accurate Supply Voltage Measurement Programmable Dual Voltage Monitors**

- ♦ SPI-/QSPI-/MICROWIRE-Compatible, 4-Wire Serial Interface

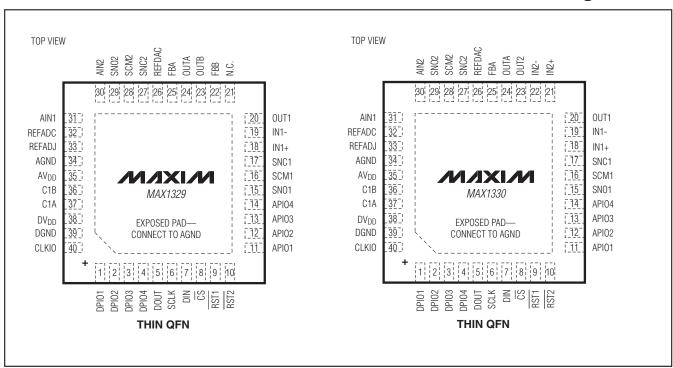

- ◆ Space-Saving, 6mm x 6mm, 40-Pin Thin QFN **Package**

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE      |

|---------------|----------------|------------------|

| MAX1329BETL+  | -40°C to +85°C | 40 Thin QFN-EP** |

| MAX1330BETL+* | -40°C to +85°C | 40 Thin QFN-EP** |

<sup>\*</sup>Future product—contact factory for availability.

Pin Configurations appear at end of data sheet.

MIXIM

<sup>\*\*</sup>EP = Exposed pad.

<sup>+</sup>Denotes a lead-free/RoHS-compliant package.

#### **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to AGND |                                         |

|--------------------------|-----------------------------------------|

| Analog Inputs to AGND    |                                         |

| <u> </u>                 | of $(AV_{DD} + 0.3V)$ or +6V            |

| Digital Inputs to DGND   | 0.3V to the lower                       |

|                          | of (DV <sub>DD</sub> + 0.3V) or +6V     |

| Analog Outputs to AGND   | 0.3V to the lower                       |

|                          | of $(AV_{DD} + 0.3V)$ or +6V            |

| Digital Outputs to DGND  | 0.3V to the lower                       |

|                          | of (DV <sub>DD</sub> + $0.3V$ ) or $6V$ |

| AGND to DGND                                          | 0.3V to +0.3V  |

|-------------------------------------------------------|----------------|

| Continuous Current into Any Pin                       | ±50mA          |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| 40-Pin Thin QFN (derate 37mW/°C above +               | 70°C)2963mW    |

| Operation Temperature Range                           | 40°C to +85°C  |

| Storage Temperature Range                             | 65°C to +150°C |

| Junction Temperature                                  |                |

| Lead Temperature (soldering, 10s)                     | +300°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(DV_{DD} = 1.8V \text{ to } 3.6V, \text{AV}_{DD} = 2.7V \text{ to } 5.5V, \text{V}_{REFDAC} = \text{V}_{REFADC} = 2.5V, \text{ external reference}; 10 \mu F \text{ capacitor at REFADC and REFDAC}; 0.01 \mu F \text{ capacitor at REFADJ}; T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                                   | SYMBOL          | CONDITIONS                                          | MIN                                  | TYP  | MAX                | UNITS             |

|---------------------------------------------|-----------------|-----------------------------------------------------|--------------------------------------|------|--------------------|-------------------|

| ADC                                         |                 |                                                     | <u>.</u>                             |      |                    |                   |

| Resolution                                  |                 | No missing codes                                    | 12                                   |      |                    | Bits              |

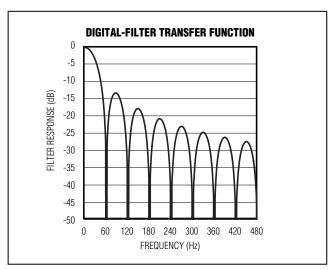

| DSP-Mode Resolution                         |                 | 256 oversampling, dither enabled                    | 16                                   |      |                    | Bits              |

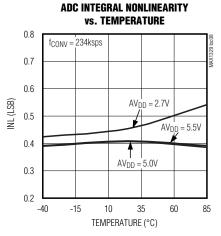

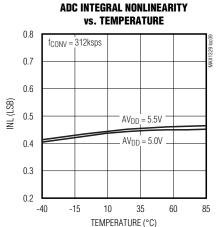

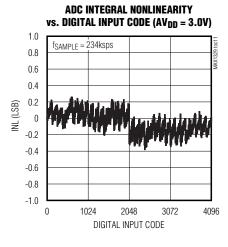

| Integral Nonlinearity                       | INL             | Normal mode (Note 1)                                |                                      |      | ±1                 | LSB <sub>12</sub> |

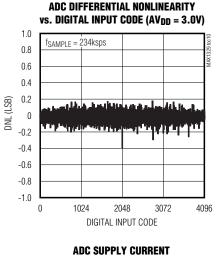

| Differential Nonlinearity                   | DNL             | Normal mode (Note 1)                                |                                      |      | ±1                 | LSB <sub>12</sub> |

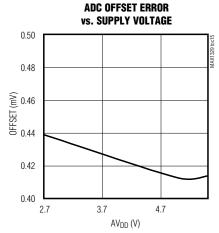

| Offset Error                                |                 | (Note 1)                                            |                                      |      | ±4                 | mV                |

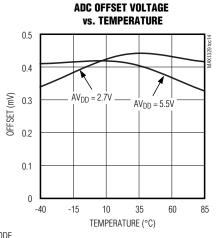

| Offset Drift                                |                 |                                                     |                                      | ±1.5 |                    | μV/°C             |

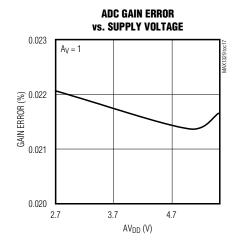

|                                             |                 | Gain = 1                                            |                                      |      | ±0.1               |                   |

| Gain Error (Excluding Reference) (Note 1)   |                 | Gain = 2, 4                                         |                                      |      | ±1.5               | % FS              |

| (Note 1)                                    |                 | Gain = 8                                            |                                      |      | ±2.5               |                   |

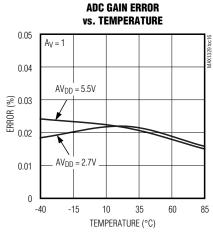

| Gain Temperature Coefficient                |                 | Excluding reference                                 |                                      | ±0.8 |                    | ppm/°C            |

| Voltage Range                               |                 | Unipolar mode, gain = 1, 2, 4, 8                    | 0                                    | +V   | REFADC/<br>Gain    | V                 |

|                                             |                 | Bipolar mode, gain = 1, 2, 4, 8                     | -V <sub>REFADC</sub> /<br>(2 x Gain) |      | REFADC/<br>x Gain) | V                 |

| Absolute Input Voltage Range                |                 |                                                     | AGND                                 |      | $AV_{DD}$          | V                 |

| Input Leakage Current into<br>Analog Inputs |                 | (Note 2)                                            |                                      | ±0.5 | ±1                 | nA                |

|                                             |                 | Gain = 1, 2                                         |                                      | 24   |                    | L                 |

| Input Capacitance                           |                 | Gain = 4, 8                                         |                                      | 48   |                    | рF                |

| A                                           |                 | Gain = 1, 2                                         | 0.6                                  |      |                    |                   |

| Acquisition Time                            | tACQ            | Gain = 4, 8                                         | 1.2                                  |      |                    | μs                |

| Conversion Time                             | tconv           | 12 clocks                                           | 2.4                                  |      |                    | μs                |

| Conversion Clock Frequency                  |                 |                                                     | 0.1                                  |      | 5.0                | MHz               |

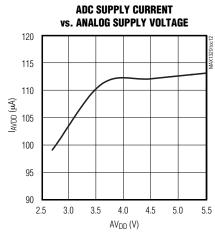

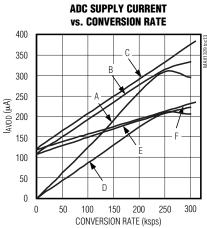

|                                             |                 | Normal operation mode,<br>ADC converting at 234ksps |                                      | 325  |                    |                   |

| ADC Supply Current (Note 3)                 |                 | Fast power-down mode,<br>ADC converting at 234ksps  |                                      | 210  |                    | μΑ                |

| Aperture Delay                              | t <sub>AD</sub> |                                                     |                                      | 30   |                    | ns                |

| , iportaro bolay                            | 'AD             |                                                     |                                      |      |                    |                   |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = 1.8V \text{ to } 3.6V, AV_{DD} = 2.7V \text{ to } 5.5V, V_{REFDAC} = V_{REFADC} = 2.5V, external reference; 10 µF capacitor at REFADC and REFDAC; 0.01 µF capacitor at REFADJ; <math>T_{A} = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_{A} = +25$ °C.)

| PARAMETER                                                       | SYMBOL         | CONDITIONS                                                                       | MIN  | TYP   | MAX              | UNITS  |

|-----------------------------------------------------------------|----------------|----------------------------------------------------------------------------------|------|-------|------------------|--------|

| Aperture Jitter                                                 | taj            |                                                                                  |      | 50    |                  | ps     |

|                                                                 |                | Gain = 1, 2; DV <sub>DD</sub> ≥ 2.7V, AV <sub>DD</sub> ≥ 5.0V                    |      |       | 312              |        |

| Comple Date                                                     |                | Gain = 4, 8; DV <sub>DD</sub> ≥ 2.7V, AV <sub>DD</sub> ≥ 5.0V                    |      |       | 263              | long   |

| Sample Rate                                                     |                | Gain = 1, 2                                                                      |      |       | 234              | ksps   |

|                                                                 |                | Gain = 4, 8                                                                      |      |       | 200              |        |

| Power-Supply Rejection                                          | PSR            | AV <sub>DD</sub> = 2.7V to 5.5V, full-scale input                                |      | ±0.06 | ±0.5             | mV/V   |

| Turn-On Time                                                    |                | Supply and reference have settled                                                |      | 1     |                  | μs     |

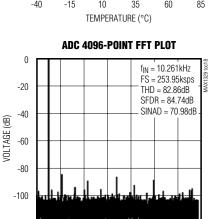

| ADC DYNAMIC ACCURACY (10)                                       | kHz sine wave  | e, V <sub>IN</sub> = 2.5V <sub>P-P</sub> , f <sub>SAMPLE</sub> = 234ksps, gain = | 1)   |       |                  |        |

| Signal-to-Noise Plus Distortion                                 | SINAD          |                                                                                  |      | 71    |                  | dB     |

| Total Harmonic Distortion                                       | THD            | Up to the 5th harmonic                                                           |      | 82    |                  | dB     |

| Spurious-Free Dynamic Range                                     | SFDR           |                                                                                  |      | 84    |                  | dB     |

| Channel-to-Channel Crosstalk                                    |                |                                                                                  |      | 100   |                  | dB     |

| Full-Power Bandwidth                                            | FPBW           | -3dB point                                                                       |      | 4     |                  | MHz    |

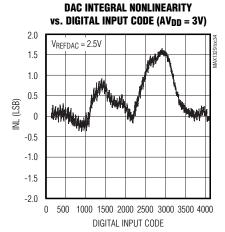

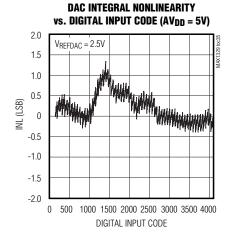

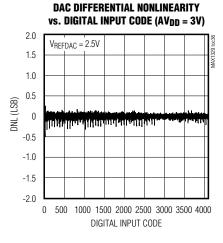

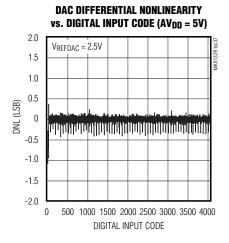

| DAC (R <sub>L</sub> = $5k\Omega$ , C <sub>L</sub> = 200pF, test | ed in unity ga | in, unless otherwise noted)                                                      |      |       |                  |        |

| Resolution                                                      |                |                                                                                  | 12   |       |                  | Bits   |

| Differential Nonlinearity                                       | DNL            | Guaranteed monotonic (Note 4)                                                    |      |       | ±1.0             | LSB    |

| Integral Nonlinearity                                           | INL            | (Note 4)                                                                         |      | ±1    | ±8               | LSB    |

| Offset Error                                                    |                | Code = 0x000 (tested at 0x032)                                                   |      | ±2.5  | ±30              | mV     |

| Offset-Error Temperature<br>Coefficient                         |                | Due to amplifier                                                                 |      | ±7    |                  | μV/°C  |

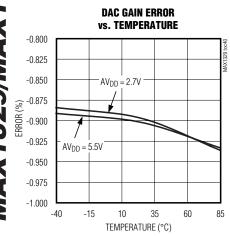

| Gain Error                                                      |                | Code = 0xFFF                                                                     |      | 0     | ±5               | % FS   |

| Gain-Error Temperature<br>Coefficient                           |                | Excluding reference drift                                                        |      | ±7    |                  | ppm/°C |

| Output Voltage Range                                            |                | No load                                                                          | AGND |       | AV <sub>DD</sub> | V      |

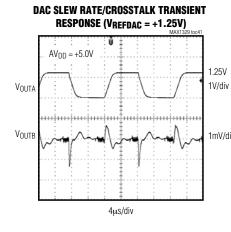

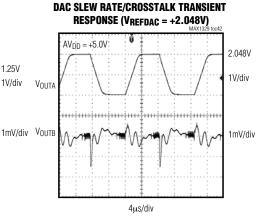

| Output Slew Rate                                                |                | $C_L = 200pF$                                                                    |      | 0.5   |                  | V/µs   |

| Output Settling Time                                            |                | Code = 0x400 to 0xC00 (Note 2)                                                   |      | 4     | 10               | μs     |

| FB_ Input Bias Current                                          |                | (Note 2)                                                                         |      | ±0.1  | 1                | nA     |

| FB_ Switch Resistance                                           |                |                                                                                  | Ì    |       | 200              | Ω      |

| FB_ Switch Turn-On/-Off Time                                    |                |                                                                                  |      | 40    |                  | ns     |

| FB_ Switch Off Isolation                                        |                | f = 10kHz                                                                        |      | 100   |                  | dB     |

| FB_ Switch Charge Injection                                     |                |                                                                                  |      | 1     |                  | рС     |

| DAC-to-DAC Crosstalk                                            |                |                                                                                  |      | 0.5   |                  | nV-s   |

| Short Circuit Current                                           |                | Sink                                                                             |      | 13    |                  | mΛ     |

| Short-Circuit Current                                           |                | Source                                                                           |      | 50    |                  | mA     |

| DC Output Impedance                                             |                | Code = 0x800                                                                     |      | 0.8   |                  | Ω      |

| Power-Up Time                                                   |                | 0.5 LSB settling to 0x800                                                        |      | 5     |                  | μs     |

| Power-Supply Rejection                                          | PSR            | AV <sub>DD</sub> = 2.7V to 5.5V                                                  |      | ±1    |                  | mV/V   |

| Charge-Pump Output Feedthrough                                  |                | Code = 0x800, buffer on, $R_L = 5k\Omega$ , $C_L = 200pF$                        |      | 100   |                  | μVRMS  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(DV<sub>DD</sub> = 1.8V to 3.6V, AV<sub>DD</sub> = 2.7V to 5.5V, V<sub>REFDAC</sub> = V<sub>REFADC</sub> = 2.5V, external reference;  $10\mu F$  capacitor at REFADC and REFDAC;  $0.01\mu F$  capacitor at REFADJ;  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                              | SYMBOL       | CONDITIONS                                        | MIN    | TYP                                  | MAX                        | UNITS           |  |

|----------------------------------------|--------------|---------------------------------------------------|--------|--------------------------------------|----------------------------|-----------------|--|

| Power-Down Output Leakage<br>Current   |              |                                                   |        |                                      | ±100                       | nA              |  |

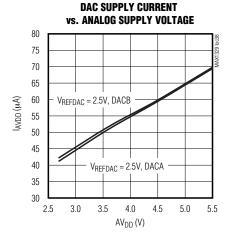

| Supply Current per DAC                 |              | No load (Note 3)                                  |        | 70                                   |                            | μΑ              |  |

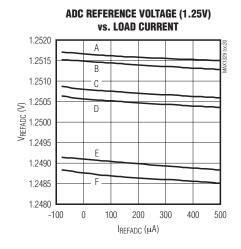

| INTERNAL REFERENCE (10µF ca            | pacitor at R | EFADC and REFDAC, 0.01μF capacitor at R           | EFADJ) |                                      |                            |                 |  |

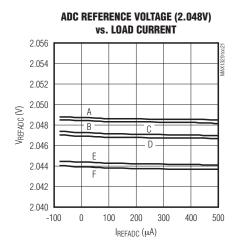

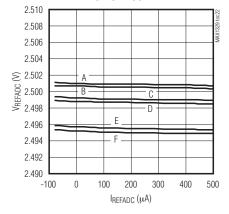

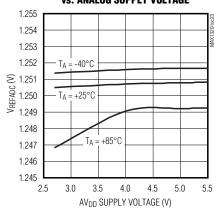

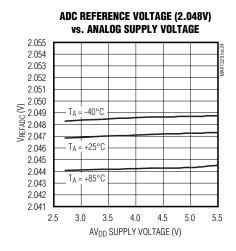

| 0                                      |              | $T_A = +25^{\circ}C$ , AREF<1:0> = DREF<1:0> = 01 | 1.225  | 1.250                                | 1.275                      |                 |  |

| Output Voltage at REFADC and REFDAC    |              | $T_A = +25^{\circ}C$ , AREF<1:0> = DREF<1:0> = 10 | 2.007  | 2.048                                | 2.089                      | V               |  |

| TIEL BAC                               |              | $T_A = +25^{\circ}C$ , AREF<1:0> = DREF<1:0> = 11 | 2.450  | 2.500                                | 2.550                      |                 |  |

| Output-Voltage Temperature             |              | (Note 2)                                          |        | ±10                                  | ±75                        | ppm/°C          |  |

| REFADC and REFDAC                      |              | Source                                            |        | 40                                   |                            | т Л             |  |

| Output Short-Circuit Current           |              | Sink                                              |        | 13                                   |                            | mA              |  |

| REFADC and REFDAC<br>Line Regulation   |              |                                                   |        | ±100                                 | ±600                       | μV/V            |  |

|                                        |              | ISOURCE = 0μA to 500μA, T <sub>A</sub> = +25°C    |        |                                      | 10                         | 24/ 4           |  |

| Load Regulation                        |              | ISINK = 0µA to 80µA, T <sub>A</sub> = +25°C       |        |                                      | 10                         | μV/μΑ           |  |

| Long-Term Stability                    |              | T <sub>A</sub> = +25°C                            |        | ±100                                 |                            | ppm/<br>1000hrs |  |

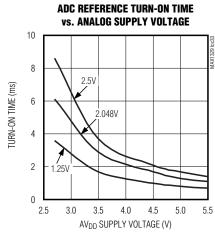

| Turn-On Time                           |              | At REFADJ                                         |        | 2                                    |                            | ms              |  |

| Turn-Off Time                          |              |                                                   |        | 100                                  |                            | ns              |  |

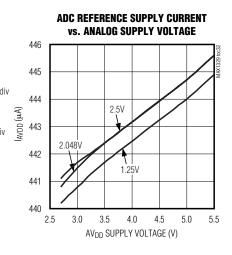

|                                        |              | Internal reference                                |        | 445                                  |                            |                 |  |

| Reference Supply Current (Note 3)      |              | REFADC buffer                                     |        | 270                                  |                            | μΑ              |  |

|                                        |              | REFDAC buffer                                     |        | 270                                  |                            | İ               |  |

| EXTERNAL REFERENCE AT REF              | ADJ          |                                                   | •      |                                      |                            |                 |  |

|                                        |              | AREF<1:0> = DREF<1:0> = 11                        | 1.225V |                                      | AV <sub>DD</sub><br>- 0.1V |                 |  |

| External Reference Input Voltage Range |              | AREF<1:0> = DREF<1:0> = 10                        | P      | 1.496V to                            |                            | V               |  |

|                                        |              | AREF<1:0> = DREF<1:0> = 01                        | A      | 2.450V to<br>AV <sub>DD</sub> - 0.1V |                            |                 |  |

| Input Resistance                       |              |                                                   | 50     | 75                                   |                            | kΩ              |  |

|                                        |              | AREF<1:0> = 01                                    |        | 1                                    |                            |                 |  |

| REFADC Buffer Gain                     |              | AREF<1:0> = 10                                    | 0.8192 |                                      |                            | V/V             |  |

|                                        |              | AREF<1:0> = 11                                    |        | 0.5                                  |                            | 1               |  |

|                                        |              | DREF<1:0> = 01                                    |        | 1                                    |                            |                 |  |

| REFDAC Buffer Gain                     |              | DREF<1:0> = 10                                    |        | 0.8192                               |                            | V/V             |  |

|                                        |              | DREF<1:0> = 11                                    |        | 0.5                                  |                            | 1               |  |

| Minimum Capacitive Bypass              |              | REFADJ to AGND                                    |        | 10                                   |                            | nF              |  |

|                                        |              |                                                   |        |                                      |                            |                 |  |

MIXIM

### **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = 1.8V \text{ to } 3.6V, \text{AV}_{DD} = 2.7V \text{ to } 5.5V, \text{V}_{REFDAC} = \text{V}_{REFADC} = 2.5V, \text{ external reference}; 10 \mu F capacitor at REFADC and REFDAC; 0.01 \mu F capacitor at REFADJ; TA = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at TA = +25°C.)$

| PARAMETER                                     | SYMBOL | CONDITIONS                                                                   | MIN  | TYP   | MAX              | UNITS |

|-----------------------------------------------|--------|------------------------------------------------------------------------------|------|-------|------------------|-------|

| EXTERNAL REFERENCE AT REF                     | ADC    |                                                                              | •    |       |                  |       |

| External Reference Input Voltage<br>Range     |        |                                                                              | AGND |       | $AV_{DD}$        | V     |

| REFADC Input Resistance                       |        |                                                                              | 50   | 75    |                  | kΩ    |

| REFADC Input Current                          |        | VREFADC = 2.5V, 300ksps                                                      |      | 30    | 40               | μΑ    |

| Turn-On Time                                  |        | REFADC buffer, CREFADC = 1µF                                                 |      | 75    |                  | μs    |

| Shutdown REFADC Input Current                 |        |                                                                              |      | 0.01  | 1.0              | μΑ    |

| Minimum Capacitive Bypass                     |        | REFADC to AGND                                                               | 10   |       |                  | μF    |

| EXTERNAL REFERENCE AT REF                     | DAC    |                                                                              |      |       |                  |       |

| REFDAC Input Voltage Range                    |        |                                                                              | AGND |       | AV <sub>DD</sub> | V     |

| DEED A Charact Desistance                     |        | MAX1329                                                                      | 64   | 90    | 180              | l.O   |

| REFDAC Input Resistance                       |        | MAX1330                                                                      | 128  | 180   | 360              | kΩ    |

| REFDAC Input Current                          |        | MAX1329, V <sub>REFDAC</sub> = 2.5V                                          |      | 28    | 86               | μА    |

|                                               |        | MAX1330, V <sub>REFDAC</sub> = 2.5V                                          |      | 14    | 43               |       |

| Turn-On Time                                  |        | REFDAC buffer                                                                |      | 75    |                  | μs    |

| Shutdown REFDAC Input Current                 |        |                                                                              |      | 0.1   | 1                | μΑ    |

| Minimum Capacitive Bypass                     |        | REFDAC to AGND                                                               | 10   |       |                  | μF    |

| MULTIPLEXER                                   |        |                                                                              |      |       |                  |       |

| Absolute Input Voltage Range                  |        |                                                                              | AGND |       | $AV_{DD}$        | V     |

| Absolute Input Leakage Current                |        | (AGND + 100mV) < V <sub>AIN</sub> _ < (AV <sub>DD</sub> - 100mV)<br>(Note 2) |      | ±0.01 | ±1               | nA    |

|                                               |        | ADC gain = 1, 2                                                              |      | 24    |                  | L     |

| Input Capacitance                             |        | ADC gain = 4, 8                                                              |      | 48    |                  | рF    |

| On Resistance                                 |        |                                                                              |      | 340   |                  | Ω     |

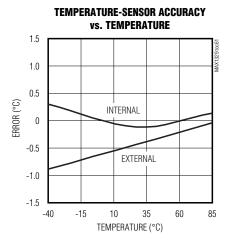

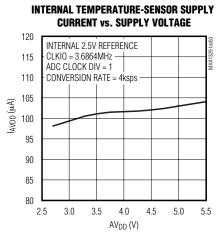

| INTERNAL TEMPERATURE SENS                     | SOR    |                                                                              |      |       |                  |       |

| Internal Sensor Measurement                   |        | T <sub>A</sub> = +25°C                                                       |      | ±0.25 |                  | °C    |

| Error (Note 5)                                |        | $T_A = -40$ °C to $+85$ °C                                                   |      |       | ±3               | -0    |

| 5                                             |        | T <sub>A</sub> = +25°C                                                       |      | ±0.4  |                  |       |

| External Sensor Measurement<br>Error (Note 5) |        | $T_A = 0$ °C to +70°C                                                        |      | ±2    |                  | °C    |

| LITOI (NOTE 3)                                |        | $T_A = -40$ °C to $+85$ °C                                                   |      | ±3    |                  |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

(DV<sub>DD</sub> = 1.8V to 3.6V, AV<sub>DD</sub> = 2.7V to 5.5V, V<sub>REFDAC</sub> = V<sub>REFADC</sub> = 2.5V, external reference;  $10\mu F$  capacitor at REFADC and REFDAC;  $0.01\mu F$  capacitor at REFADJ;  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                          | SYMBOL                                | CONDITIONS                                                     | MIN  | TYP   | MAX   | UNITS                                 |  |

|----------------------------------------------------|---------------------------------------|----------------------------------------------------------------|------|-------|-------|---------------------------------------|--|

| Temperature Resolution                             |                                       | VREFADC = 2.5V                                                 |      | 1/8   |       | °C/LSB                                |  |

| External-Diode Drive Ratio                         |                                       | IDRIVEMIN = 4μA, IDRIVEMAX = 68μA                              |      | 17:1  |       |                                       |  |

| Temperature-Sensor Supply Current                  |                                       | Not including ADC current (Note 3)                             |      | 100   |       | μА                                    |  |

| Temperature-Sensor Conversion Time                 |                                       | 307 clocks per measurement, master clock = 5.00MHz             |      | 65    |       | μs                                    |  |

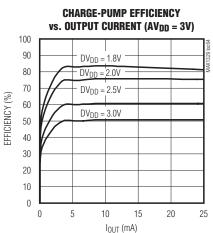

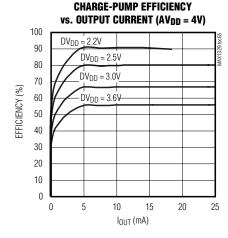

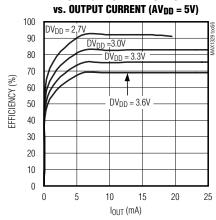

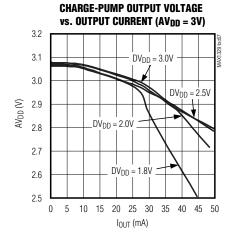

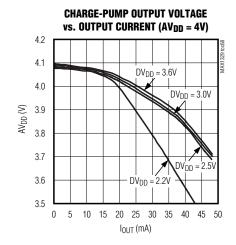

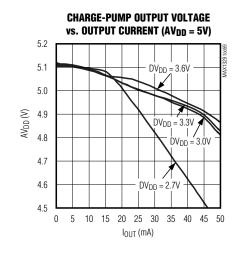

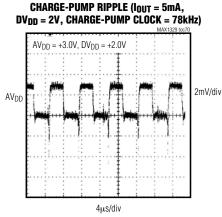

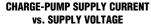

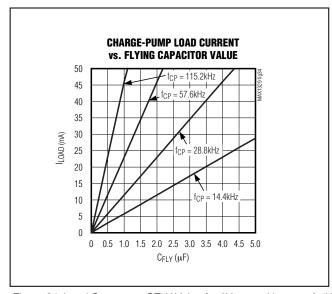

| CHARGE PUMP                                        | •                                     |                                                                |      |       |       |                                       |  |

| Input Voltage                                      | DV <sub>DD</sub>                      |                                                                | 1.8  |       | 3.6   | V                                     |  |

|                                                    |                                       | $DV_{DD} = 1.8V \text{ to } 3.0V, VM2CP < 2:0 > = 001$         | 2.85 | 3.0   | 3.20  |                                       |  |

| No-Load Output Voltage                             | $AV_{DD}$                             | DV <sub>DD</sub> = 2.2V to 3.6V, VM2CP<2:0> = 010              | 3.75 | 4.0   | 4.30  | V                                     |  |

|                                                    |                                       | DV <sub>DD</sub> = 2.7V to 3.6V, VM2CP<2:0> = 011              | 4.80 | 5.0   | 5.40  |                                       |  |

| Output Current                                     |                                       | Including internal current (Table 32)                          | 25   |       |       | mA                                    |  |

| No-Load Supply Current                             |                                       | DV <sub>DD</sub> = 2.7V, AV <sub>DD</sub> = 4V, 39kHz clock    |      | 250   |       | μΑ                                    |  |

| Switching Frequency                                |                                       |                                                                | 39   |       | 78    | kHz                                   |  |

| Switch Turn-On/-Off Time                           |                                       | Between DV <sub>DD</sub> to AV <sub>DD</sub> , charge pump off |      | 40    |       | ns                                    |  |

| Switch Impedance                                   |                                       | Shorts DV <sub>DD</sub> to AV <sub>DD</sub> , charge pump off  |      | 25    | 50    | Ω                                     |  |

| Efficiency                                         |                                       | 25mA load, $DV_{DD} = 1.8V$ , $AV_{DD} = 3.0V$ , 39kHz clock   |      | 80    |       | %                                     |  |

| DV <sub>DD</sub> VOLTAGE MONITOR (VM               | 1)                                    |                                                                | I.   |       |       | •                                     |  |

| Supply Voltage Range                               |                                       |                                                                | 1.0  |       | 3.6   | V                                     |  |

| Tria Thurshald (D) ( Falling)                      | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | $VM1<1:0> = 0x, \overline{RST1} input$                         | 1.80 | 1.865 | 1.93  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |  |

| Trip Threshold (DV <sub>DD</sub> Falling)          | V <sub>DTH</sub>                      | $VM1<1:0> = x0, \overline{RST2}$ input                         | 2.65 | 2.750 | 2.90  | V                                     |  |

| I bushanasia                                       |                                       | $VM1<1:0> = 0x, \overline{RST1} input$                         |      | 15    |       | \/                                    |  |

| Hysteresis                                         | VDHYS                                 | $VM1<1:0> = x0, \overline{RST2} \text{ input}$                 |      | 22.5  |       | mV                                    |  |

| Reset Timeout Period                               |                                       | V <sub>DVDD</sub> = V <sub>DTH</sub> + V <sub>DHYS</sub>       |      | 170   |       | ms                                    |  |

| Turn-On Time                                       |                                       | DV <sub>DD</sub> = 1.8V, enabled by VM1 <1:0>                  |      | 2     |       | ms                                    |  |

| AV <sub>DD</sub> VOLTAGE MONITOR (VM:              | 2)                                    |                                                                |      |       |       |                                       |  |

| Supply Voltage Range                               |                                       |                                                                | 1.0  |       | 5.5   | V                                     |  |

|                                                    |                                       | VM2CP<1:0> = 01                                                | 2.53 | 2.775 | 2.975 |                                       |  |

| Trip Threshold (AV <sub>DD</sub> Falling) (Note 6) | V <sub>ATH</sub>                      | VM2CP<1:0> = 10                                                | 3.4  | 3.700 | 3.925 | V                                     |  |

| (NOLG U)                                           |                                       | VM2CP<1:0> = 11                                                | 4.25 | 4.625 | 4.925 |                                       |  |

|                                                    |                                       | VM2CP<1:0> = 01                                                |      | 22.5  |       |                                       |  |

| Hysteresis                                         | VAHYS                                 | VM2CP<1:0> = 10                                                |      | 30    |       | mV                                    |  |

|                                                    |                                       | VM2CP<1:0> = 11                                                |      | 37.5  |       |                                       |  |

|                                                    |                                       |                                                                |      |       |       |                                       |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = 1.8V \text{ to } 3.6V, AV_{DD} = 2.7V \text{ to } 5.5V, V_{REFDAC} = V_{REFADC} = 2.5V, external reference; 10 µF capacitor at REFADC and REFDAC; 0.01 µF capacitor at REFADJ; <math>T_{A} = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_{A} = +25$ °C.)

| PARAMETER                          | SYMBOL                   | CONDITIONS                                                              | MIN    | TYP    | MAX                       | UNITS             |

|------------------------------------|--------------------------|-------------------------------------------------------------------------|--------|--------|---------------------------|-------------------|

| Turn-On Time                       |                          | AV <sub>DD</sub> = 2.7V, enabled by VM2CP<1:0>                          |        | 2      |                           | ms                |

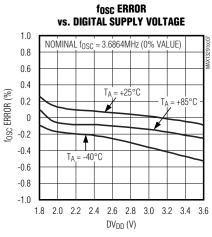

| INTERNAL OSCILLATOR                | •                        | •                                                                       |        |        |                           |                   |

| Clock Frequency                    |                          | TA = TMIN to TMAX                                                       | 3.5758 | 3.6864 | 3.7970                    | MHz               |

| Turn-Off Delay                     | İ                        | Using clock at CLKIO pin, ODLY = 1                                      |        | 1024   |                           | Clocks            |

| Turn-On Time                       |                          |                                                                         |        | 200    |                           | ns                |

| Supply Current                     |                          | (Note 7)                                                                |        | 120    |                           | μΑ                |

| SWITCHES (SPDT)                    | •                        | ·                                                                       | •      |        |                           | •                 |

| 0.0                                |                          | AV <sub>DD</sub> = 2.7V to 5.5V                                         |        | 140    | 200                       |                   |

| On Resistance                      |                          | AV <sub>DD</sub> = 4.5V to 5.5V                                         |        | 90     | 120                       | Ω                 |

| On-Resistance Match                |                          |                                                                         |        | 15     |                           | Ω                 |

| On-Resistance Flatness             |                          | Over analog voltage range                                               |        | 12     |                           | Ω                 |

| Analog Voltage Range               |                          |                                                                         | AGND   |        | $AV_{DD}$                 | V                 |

| Turn-On/-Off Time                  |                          | Break-before-make for SPDT configuration                                |        | 50     |                           | ns                |

| Leakage Current                    |                          | AGND + 100mV < V <sub>SN</sub> _ < AV <sub>DD</sub> - 100mV<br>(Note 2) |        | 0.08   | ±1                        | nA                |

| Off Isolation                      |                          | f = 10kHz                                                               |        | 100    |                           | dB                |

| Charge Injection                   |                          |                                                                         |        | 1      |                           | рС                |

| Input Capacitance                  |                          |                                                                         |        | 2      |                           | pF                |

| OPERATIONAL AMPLIFIER (RL          | = 10kΩ, C <sub>L</sub> = | 200pF)                                                                  | - IL   |        |                           |                   |

| Input Bias Current                 |                          | (Note 2)                                                                |        | 0.3    | ±1                        | nA                |

| Input Offset Voltage               | Vos                      |                                                                         |        | 2      | ±20                       | mV                |

| Input Offset Drift                 | ΔVos                     |                                                                         |        | ±10    |                           | μV/°C             |

| Common-Mode Rejection Ratio        | CMRR                     | AGND + 100mV < V <sub>CM</sub> < AV <sub>DD</sub> - 100mV               |        | 75     |                           | dB                |

| Phase Margin                       |                          |                                                                         |        | 60     |                           | degrees           |

| Charge-Pump Output<br>Feedthrough  |                          |                                                                         |        | 100    |                           | µV <sub>P-P</sub> |

| Common-Mode Input Voltage<br>Range |                          |                                                                         | AGND   |        | AV <sub>DD</sub>          | V                 |

|                                    |                          | No load                                                                 | AGND   |        | AV <sub>DD</sub>          |                   |

| Output Voltage Range               |                          | 10kΩ load                                                               | 0.1    |        | AV <sub>DD</sub><br>- 0.1 | V                 |

|                                    |                          | 100kΩ load                                                              | 0.1    |        | AV <sub>DD</sub><br>- 0.1 |                   |

| Gain Bandwidth Product             |                          |                                                                         |        | 1      |                           | MHz               |

| Slew Rate                          |                          |                                                                         |        | 0.5    |                           | V/µs              |

|                                    |                          | AV <sub>DD</sub> = 2.7V to 5.5V                                         |        | 140    | 200                       | -                 |

| OSW_ Switch Resistance             |                          | AV <sub>DD</sub> = 4.5V to 5.5V                                         |        | 90     | 120                       | Ω                 |

| OSW_ Switch Turn-On/-Off Time      |                          |                                                                         |        | 50     |                           | ns                |

|                                    | <u> </u>                 | 1                                                                       | 1      |        |                           | 1                 |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = 1.8V \text{ to } 3.6V, \text{AV}_{DD} = 2.7V \text{ to } 5.5V, \text{V}_{REFDAC} = \text{V}_{REFADC} = 2.5V, \text{ external reference}; 10 \mu F \text{ capacitor at REFADC and REFDAC}; 0.01 \mu F \text{ capacitor at REFADJ}; T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_{A} = +25^{\circ}\text{C.})$

| PARAMETER                                       | SYMBOL          | CONDITIONS                                               | MIN                       | TYP   | MAX                    | UNITS             |

|-------------------------------------------------|-----------------|----------------------------------------------------------|---------------------------|-------|------------------------|-------------------|

| OSW_ Switch Charge Injection                    |                 |                                                          |                           | 1     |                        | рС                |

| Input Noise Voltage Density                     |                 | $f_{IN} = 1kHz$                                          |                           | 330   |                        | nV/√Hz            |

| Input Noise Voltage                             |                 | $f_{IN}$ = 0.1Hz to 10Hz                                 |                           | 9     |                        | μV <sub>RMS</sub> |

| Power-Down Output Leakage                       |                 |                                                          |                           |       | ±10                    | nA                |

| Power-Supply Rejection Ratio                    |                 | $AV_{DD} = 2.7V \text{ to } 5.5V$                        | 65                        | 100   |                        | dB                |

| Supply Current per Amplifier                    |                 | (Note 3)                                                 |                           | 70    |                        | μΑ                |

| Turn-On Time                                    |                 |                                                          |                           | 5     |                        | μs                |

| Short-Circuit Current                           |                 | Source                                                   |                           | 50    |                        | mA                |

| Short-Circuit Current                           |                 | Sink                                                     |                           | 13    |                        | IIIA              |

| DC Output Impedance                             |                 | $A_V = 1V/V$                                             |                           | 0.2   |                        | Ω                 |

| DIGITAL INPUTS (DIN, SCLK, CS                   | )               |                                                          |                           |       |                        | _                 |

| Input High Voltage                              | V <sub>IH</sub> |                                                          | 0.7 x<br>DV <sub>DD</sub> |       |                        | V                 |

| Input Low Voltage                               | VIL             |                                                          |                           |       | 0.3 x DV <sub>DD</sub> | V                 |

| Input Hysteresis                                |                 | $DV_{DD} = 3V$                                           |                           | 200   |                        | mV                |

| Input Leakage Current                           |                 | V <sub>IN</sub> = 0 or DV <sub>DD</sub>                  |                           | ±0.01 | ±10                    | μΑ                |

| DIGITAL OUTPUTS (DOUT, RST1                     | , RST2)         |                                                          |                           |       |                        |                   |

| Output Low Voltage                              | Vol             | $I_{SINK} = 1$ mA, $DV_{DD} = 2.7$ V to 3.6V             |                           |       | 0.4                    | V                 |

| Output Low Voltage                              | VOL             | $I_{SINK} = 200\mu A$ , $DV_{DD} = 1.8V$ to 3.6V         |                           |       | 0.4                    | V                 |

| Outhout Himb Voltage                            | \/-··           | ISOURCE = 0.2mA, DV <sub>DD</sub> = 2.7V to 3.6V         | 0.8 x<br>DV <sub>DD</sub> |       |                        | V                 |

| Output High Voltage                             | Voн             | $I_{SOURCE} = 100 \mu A$ , $DV_{DD} = 1.8 V$ to 3.6 V    | 0.8 x<br>DV <sub>DD</sub> |       |                        | V                 |

| DOUT Three-State Leakage                        |                 |                                                          |                           | ±0.01 | ±10                    | μΑ                |

| DOUT Three-State Capacitance                    |                 | (Note 2)                                                 |                           |       | 15                     | рF                |

| RST1, RST2 Open-Drain Output                    |                 | $I_{SINK} = 1$ mA, $DV_{DD} = 2.7$ V to 3.6V             |                           |       | 0.4                    | V                 |

| Low Voltage                                     |                 | $I_{SINK} = 200\mu A$ , $DV_{DD} = 1.8V$ to 3.6V         |                           |       | 0.4                    | V                 |

| RST1, RST2 Open-Drain Output<br>Leakage Current |                 | (Note 2)                                                 |                           | 0.13  | 100                    | nA                |

| DIGITAL I/O (DPIO1-DPIO4, CLK                   | IO)             | •                                                        | •                         |       |                        | •                 |

| Output Low Voltogs                              |                 | $I_{SINK}$ = 2mA, $DV_{DD}$ = 2.7V to 3.6V               |                           |       | 0.4                    | V                 |

| Output Low Voltage                              |                 | I <sub>SINK</sub> = 1mA, DV <sub>DD</sub> = 1.8V to 3.6V |                           |       | 0.4                    | ]                 |

| Outhout Himb Voltage                            |                 | ISOURCE = 2mA, DVDD = 2.7V to 3.6V                       | 0.8 x<br>DV <sub>DD</sub> |       |                        | V                 |

| Output High Voltage                             |                 | ISOURCE = 1mA, DVDD = 1.8V to 3.6V                       | 0.8 x<br>DV <sub>DD</sub> |       |                        | V                 |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = 1.8V \text{ to } 3.6V, \text{AV}_{DD} = 2.7V \text{ to } 5.5V, \text{V}_{REFDAC} = \text{V}_{REFADC} = 2.5V, \text{ external reference}; 10 \mu F capacitor at REFADC and REFDAC; 0.01 \mu F capacitor at REFADJ; TA = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at TA = +25°C.)$

| PARAMETER                             | SYMBOL | CONDITIONS                                               | MIN                       | TYP   | MAX                                                              | UNITS |

|---------------------------------------|--------|----------------------------------------------------------|---------------------------|-------|------------------------------------------------------------------|-------|

| Input High Voltage                    |        |                                                          | 0.7 x<br>DV <sub>DD</sub> |       |                                                                  | V     |

| Input Low Voltage                     |        | DPIO1-DPIO4                                              |                           |       | 0.3 x<br>DV <sub>DD</sub>                                        | V     |

| Input Low Voltage                     |        | CLKIO                                                    |                           |       | 0.25 x<br>DV <sub>DD</sub>                                       | V     |

| Input Hysteresis                      |        | DV <sub>DD</sub> = 3V                                    |                           | 110   |                                                                  | mV    |

| Three-State Leakage                   |        |                                                          |                           | ±0.01 | ±1                                                               | μΑ    |

| Three-State Capacitance               |        | (Note 2)                                                 |                           |       | 15                                                               | рF    |

| DPIO_ Pullup Resistance               |        |                                                          |                           | 0.5   |                                                                  | МΩ    |

| ANALOG I/O (APIO1-APIO4)              | - 1    |                                                          | l.                        |       |                                                                  |       |

|                                       |        | I <sub>SINK</sub> = 2mA, AV <sub>DD</sub> = 2.7V to 5.5V |                           |       | 0.4                                                              |       |

| Output Low Voltage                    |        | I <sub>SINK</sub> = 1mA, AV <sub>DD</sub> = 1.8V to 5.5V |                           |       | 0.4                                                              | V     |

| Output High Voltage                   |        | ISOURCE = 2mA, AVDD = 2.7V to 5.5V                       | 0.8 x<br>AV <sub>DD</sub> |       |                                                                  | · V   |

|                                       |        | ISOURCE = 1mA, AVDD = 1.8V to 5.5V                       | 0.8 x<br>AV <sub>DD</sub> |       |                                                                  |       |

| Input High Voltage                    |        | AV <sub>DD</sub> = 2.7V to 5.5V                          | 0.7 x<br>AV <sub>DD</sub> |       |                                                                  |       |

| Input High Voltage                    |        | $AV_{DD} = DV_{DD} = 1.8V \text{ to } 3.6V$              | 0.7 x<br>AV <sub>DD</sub> |       |                                                                  | · V   |

|                                       |        | AV <sub>DD</sub> = 2.7V to 5.5V                          |                           |       | 0.3 x<br>AV <sub>DD</sub>                                        | .,    |

| Input Low Voltage                     |        | AV <sub>DD</sub> = DV <sub>DD</sub> = 1.8V to 3.6V       |                           |       | 0.3 x<br>AV <sub>DD</sub>                                        | V     |

|                                       |        | $AV_{DD} = 3V$                                           |                           | 120   | 0.3 x<br>DVDD<br>0.25 x<br>DVDD<br>±1<br>15<br>0.4<br>0.4<br>0.4 |       |

| Input Hysteresis                      |        | $AV_{DD} = 5V$                                           |                           | 160   |                                                                  | mV    |

| Three-State Leakage                   |        |                                                          |                           | ±0.01 | ±10                                                              | μΑ    |

| Three-State Capacitance               |        | (Note 2)                                                 |                           |       | 15                                                               | рF    |

| Pullup Resistance                     |        |                                                          |                           | 0.5   |                                                                  | MΩ    |

| POWER REQUIREMENTS                    |        |                                                          | <u> </u>                  |       |                                                                  |       |

| DV <sub>DD</sub> Supply Voltage Range |        |                                                          | 1.8                       |       | 3.6                                                              | V     |

| AV <sub>DD</sub> Supply Voltage Range |        |                                                          | 2.7                       |       | 5.5                                                              | V     |

|                                       |        | Run (all on, except charge pump)                         |                           | 3.75  | 7.5                                                              | mA    |

| Supply Current (Note 8)               |        | Sleep (1.8V or 2.7V monitor on)                          |                           | 1     | 2.5                                                              | μΑ    |

| Shutdown Current                      |        | All off                                                  |                           | 0.5   | 1                                                                | μΑ    |

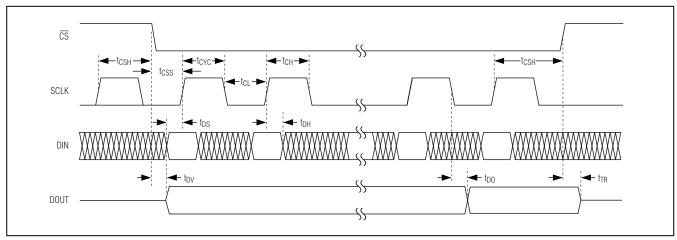

#### **TIMING CHARACTERISTICS**

(DV<sub>DD</sub> = 1.8V to 3.6V, AV<sub>DD</sub> = 2.7V to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                           | SYMBOL           | CONDITIONS                                                                   | MIN                    | TYP       | MAX                  | UNITS   |

|-----------------------------------------------------|------------------|------------------------------------------------------------------------------|------------------------|-----------|----------------------|---------|

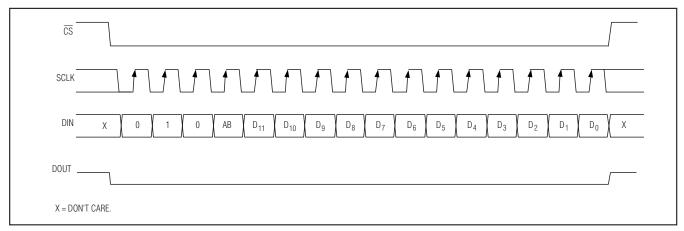

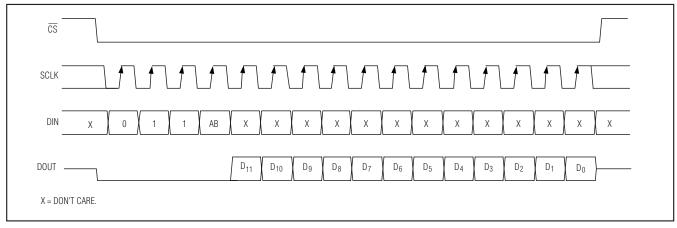

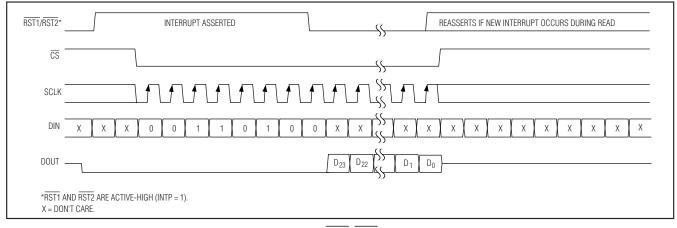

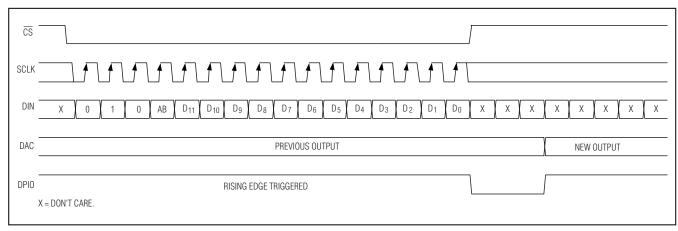

| SERIAL-INTERFACE TIMING PAR                         | RAMETERS (       | (DV <sub>DD</sub> = 2.7V to 3.6V) (Figures 1 and 2)                          |                        |           |                      |         |

| SCLK Operating Frequency                            | f <sub>OP</sub>  |                                                                              | 0                      |           | 20                   | MHz     |

| SCLK Cycle Time                                     | t <sub>CYC</sub> |                                                                              | 50                     |           |                      | ns      |

| DIN to SCLK Setup                                   | t <sub>DS</sub>  |                                                                              | 15                     |           |                      | ns      |

| DIN to SCLK Hold                                    | t <sub>DH</sub>  |                                                                              | 0                      |           |                      | ns      |

| SCLK Fall to Output Data Valid                      | t <sub>DO</sub>  |                                                                              |                        |           | 20                   | ns      |

| CS Fall to Output Enable                            | t <sub>DV</sub>  |                                                                              |                        |           | 24                   | ns      |

| CS Rise to Output Disable                           | t <sub>TR</sub>  |                                                                              |                        |           | 24                   | ns      |

| CS to SCLK Rise Setup                               | t <sub>CSS</sub> |                                                                              | 15                     |           |                      | ns      |

| CS to SCLK Rise Hold                                | t <sub>CSH</sub> |                                                                              | 0                      |           |                      | ns      |

| SCLK Pulse-Width High                               | t <sub>CH</sub>  |                                                                              | 20                     |           |                      | ns      |

| SCLK Pulse-Width Low                                | t <sub>CL</sub>  |                                                                              | 20                     |           |                      | ns      |

| SERIAL-INTERFACE TIMING PAF                         | RAMETERS (       | (DV <sub>DD</sub> = 1.8V to 3.6V) (Figures 1 and 2)                          |                        |           |                      |         |

| SCLK Operating Frequency                            | f <sub>OP</sub>  |                                                                              | 0                      |           | 10                   | MHz     |

| SCLK Cycle Time                                     | t <sub>CYC</sub> |                                                                              | 100                    |           |                      | ns      |

| DIN to SCLK Setup                                   | t <sub>DS</sub>  |                                                                              | 30                     |           |                      | ns      |

| DIN to SCLK Hold                                    | t <sub>DH</sub>  |                                                                              | 0                      |           |                      | ns      |

| SCLK Fall to Output Data Valid                      | t <sub>DO</sub>  |                                                                              |                        |           | 40                   | ns      |

| CS Fall to Output Enable                            | t <sub>DV</sub>  |                                                                              |                        |           | 48                   | ns      |

| CS Rise to Output Disable                           | t <sub>TR</sub>  |                                                                              |                        |           | 48                   | ns      |

| CS to SCLK Rise Setup                               | t <sub>CSS</sub> |                                                                              | 30                     |           |                      | ns      |

| CS to SCLK Rise Hold                                | t <sub>CSH</sub> |                                                                              | 0                      |           |                      | ns      |

| SCLK Pulse-Width High                               | t <sub>CH</sub>  |                                                                              | 40                     |           |                      | ns      |

| SCLK Pulse-Width Low                                | t <sub>CL</sub>  |                                                                              | 40                     |           |                      | ns      |

| DIGITAL PROGRAMMABLE I/O T                          | IMING PARA       | AMETERS (DPIO1-DPIO4, DV <sub>DD</sub> = 2.7V to 3.6                         | V, C <sub>L</sub> = 20 | pF)       |                      |         |

| SPI Write to DPIO Output Valid                      | t <sub>SD</sub>  | From last SCLK rising edge                                                   |                        |           | 50                   | ns      |

| DPIO Rise/Fall Input to Interrupt                   | t <sub>DI</sub>  | Interrupt programmed on RST1 and/or                                          |                        |           | 55                   | ns      |

| Asserted Delay                                      |                  | RST2, corresponding status bits unmasked                                     |                        |           |                      | 110     |

| DPIO Input to Analog Block Delay                    | t <sub>DA</sub>  | When controlling ADC, DACs, or switches                                      |                        | 40        |                      | ns      |

| DIGITAL PROGRAMMABLE I/O T                          | IMING PARA       | AMETERS (DPIO1-DPIO4, $DV_{DD} = 1.8V$ to 3.6                                | $V, C_L = 20$          | pF)       |                      |         |

| SPI Write to DPIO Output Valid                      | t <sub>SD</sub>  | From last SCLK rising edge                                                   |                        |           | 100                  | ns      |

| DPIO Rise/Fall Input to Interrupt<br>Asserted Delay | t <sub>DI</sub>  | Interrupt programmed on RST1 and/or RST2, corresponding status bits unmasked |                        |           | 150                  | ns      |

| DPIO Input to Analog Block Delay                    | t <sub>DA</sub>  | When controlling ADC, DACs, or switches                                      |                        | 50        |                      | ns      |

|                                                     |                  | AMETERS (APIO1-APIO4, DV <sub>DD</sub> = 2.7V to 3.6                         | SV, AV <sub>DD</sub> : | = 2.7V to | 5.5V, C <sub>L</sub> | = 20pF) |

| SPI Write to APIO Output Valid                      | t <sub>SD</sub>  | From last SCLK rising edge                                                   |                        |           | 50                   | ns      |

| APIO Rise/Fall Input to Interrupt<br>Asserted Delay | t <sub>DI</sub>  | Interrupt programmed on RST1 and/or RST2, corresponding status bits unmasked |                        |           | 50                   | ns      |

| CS to APIO4 Propagation Delay                       | t <sub>DCA</sub> | AP4MD<1:0> = 11                                                              | 1                      |           | 35                   | 1       |

\_ M/XI/M

#### **TIMING CHARACTERISTICS (continued)**

(DV<sub>DD</sub> = 1.8V to 3.6V, AV<sub>DD</sub> = 2.7V to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                                                                                                                        | SYMBOL           | CONDITIONS                                                                   | MIN | TYP | MAX | UNITS |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------|-----|-----|-----|-------|--|--|

| SCLK to APIO3 Propagation Delay                                                                                                                  | t <sub>DSA</sub> | AP3MD<1:0> = 11, $\overline{CS}$ is high                                     |     |     | 30  | ns    |  |  |

| DIN to APIO2 Propagation Delay                                                                                                                   | t <sub>DDA</sub> | AP2MD<1:0> = 11, $\overline{CS}$ is high                                     |     |     | 25  | ns    |  |  |

| APIO1 to DOUT Propagation<br>Delay                                                                                                               | t <sub>DAD</sub> | AP1MD<1:0> = 11, $\overline{CS}$ is high                                     |     |     | 20  | ns    |  |  |

| SPI-Mode Propagation Delay<br>Matching                                                                                                           | t <sub>DM</sub>  | Among APIO4, APIO3, APIO2, and APIO1                                         |     | ±10 | ns  |       |  |  |

| ANALOG PROGRAMMABLE I/O TIMING PARAMETERS (APIO1–APIO4, DV <sub>DD</sub> = 1.8V to 3.6V, AV <sub>DD</sub> = 2.7V to 5.5V, C <sub>L</sub> = 20pF) |                  |                                                                              |     |     |     |       |  |  |

| SPI Write to APIO Output Valid                                                                                                                   | t <sub>SD</sub>  | From last SCLK rising edge                                                   |     |     | 100 | ns    |  |  |

| APIO Rise/Fall Input to Interrupt<br>Asserted Delay                                                                                              | t <sub>DI</sub>  | Interrupt programmed on RST1 and/or RST2, corresponding status bits unmasked |     |     | 175 | ns    |  |  |

| CS to APIO4 Propagation Delay                                                                                                                    | t <sub>DCA</sub> | AP4MD<1:0> = 11                                                              |     |     | 60  | ns    |  |  |

| SCLK to APIO3 Propagation<br>Delay                                                                                                               | t <sub>DSA</sub> | AP3MD<1:0> = 11, $\overline{CS}$ is high                                     |     |     | 50  | ns    |  |  |

| DIN to APIO2 Propagation Delay                                                                                                                   | t <sub>DDA</sub> | AP2MD<1:0> = 11, $\overline{CS}$ is high                                     |     |     | 50  | ns    |  |  |

| APIO1 to DOUT Propagation<br>Delay                                                                                                               | t <sub>DAD</sub> | AP1MD<1:0> = 11, $\overline{CS}$ is high                                     |     | 80  | ns  |       |  |  |

| SPI-Mode Propagation Delay<br>Matching                                                                                                           | <sup>t</sup> DM  | Among APIO4, APIO3, APIO2, and APIO1 ±30                                     |     | ±30 | ns  |       |  |  |

- Note 1: ADC INL and DNL, offset, and gain are tested at DV<sub>DD</sub> = 1.8V, AV<sub>DD</sub> = 2.7V, f<sub>SAMPLE</sub> = 234ksps to guarantee performance at f<sub>SAMPLE</sub> = 312ksps, DV<sub>DD</sub> ≥ 2.7V and AV<sub>DD</sub> ≥ 5.0V.

- Note 2: Guaranteed by design. Not production tested.

- Note 3: AVDD supply current contribution for this module.

- Note 4: DNL and INL are measured between code 115 and 4095.

- Note 5: Temperature sensor accuracy is tested using a 2.5084V reference applied to REFADJ.

- **Note 6:** The maximum trip levels for the AV<sub>DD</sub> monitor are 5% below the typical charge-pump output value. The charge-pump output voltage and the trip thresholds track to prevent tripping at -5% below the typical charge-pump output value.

- **Note 7:** DV<sub>DD</sub> supply current contribution for this module.

- **Note 8:** The normal operation and sleep mode supply currents are measured with no load on DOUT, SCLK idle, and all digital inputs at DGND or DV<sub>DD</sub>. CLKIO runs in normal mode operation and idle in sleep mode.

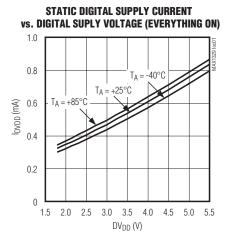

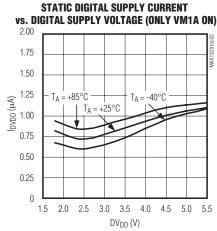

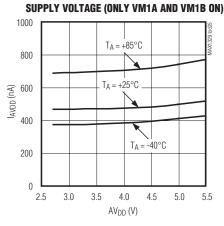

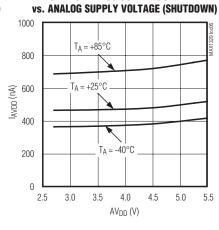

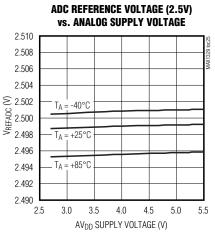

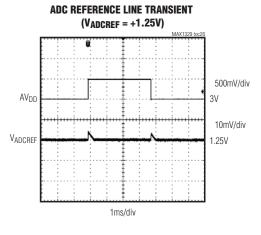

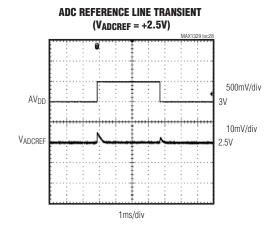

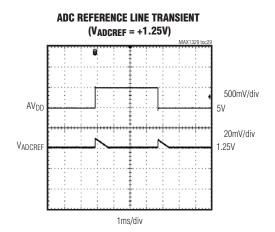

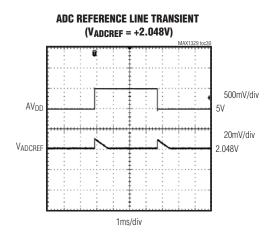

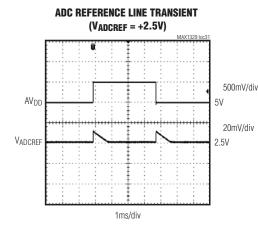

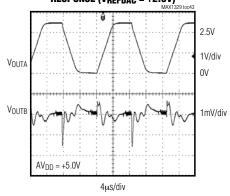

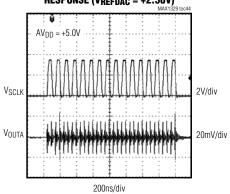

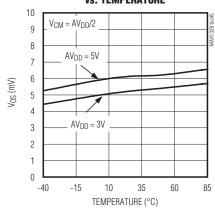

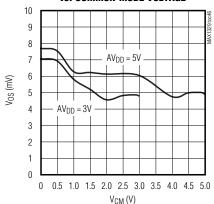

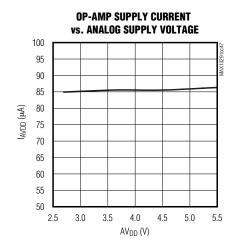

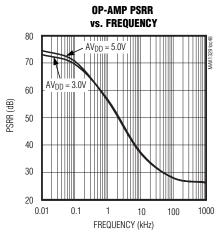

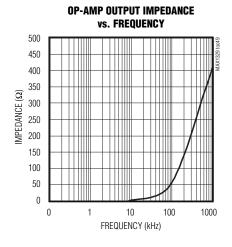

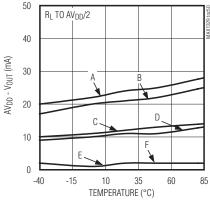

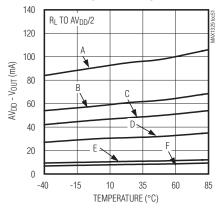

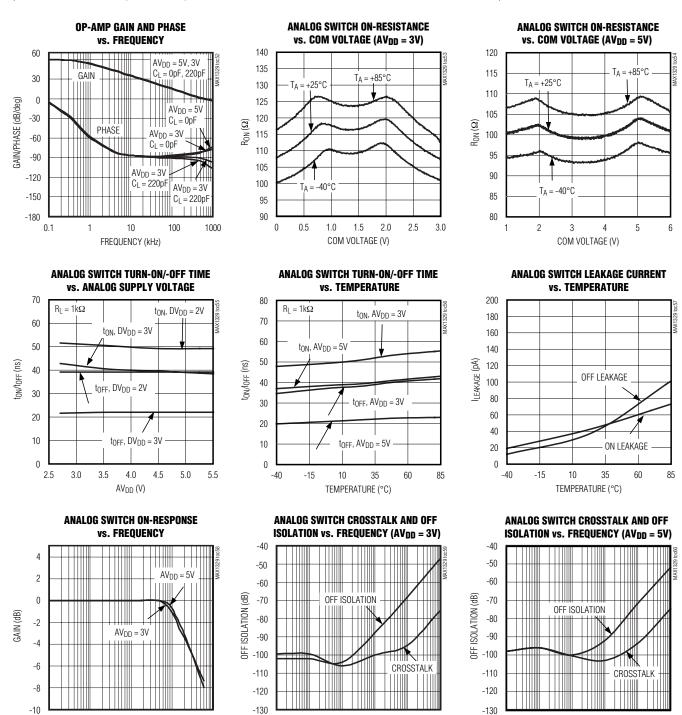

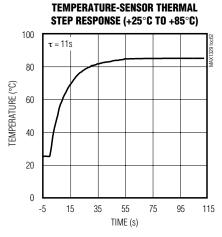

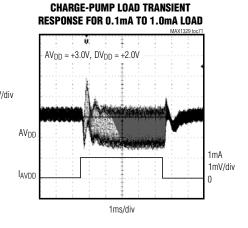

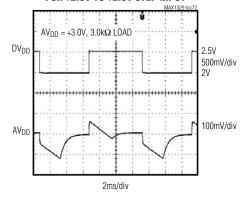

### Typical Operating Characteristics

(AVDD = 5.0V, VREFADC = VREFDAC = 2.5V for DVDD = 3.0V; TA = +25°C, unless otherwise noted.)

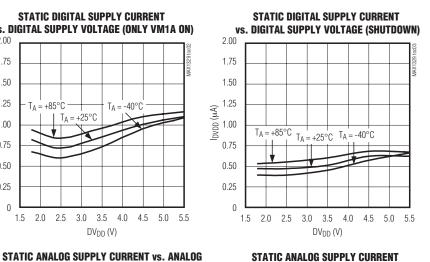

### Typical Operating Characteristics (continued)

(AVDD = 5.0V, VREFADC = VREFDAC = 2.5V for DVDD = 3.0V; TA = +25°C, unless otherwise noted.)

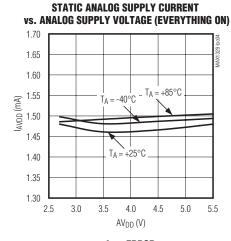

### Typical Operating Characteristics (continued)

(AVDD = 5.0V, VREFADC = VREFDAC = 2.5V for DVDD = 3.0V; TA = +25°C, unless otherwise noted.)

FREQUENCY (kHz)

0 20 40 60 80 100 120

### **Typical Operating Characteristics (continued)**

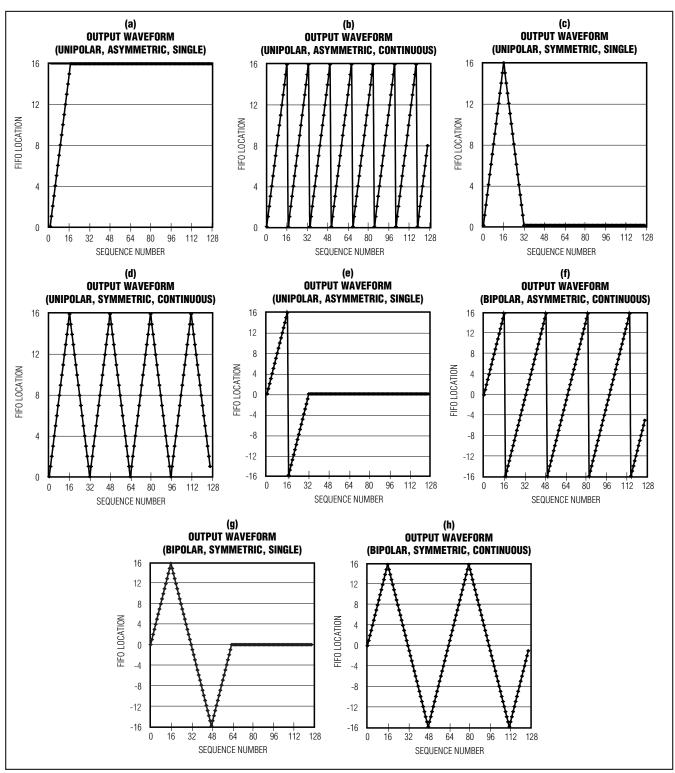

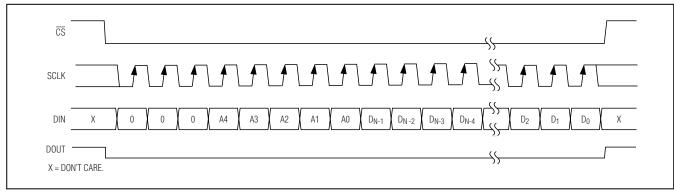

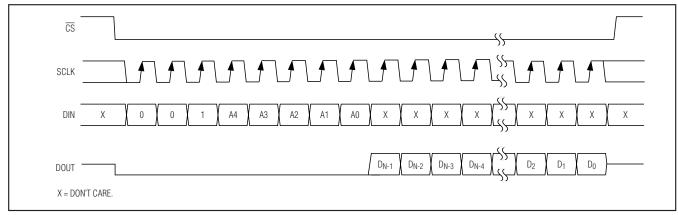

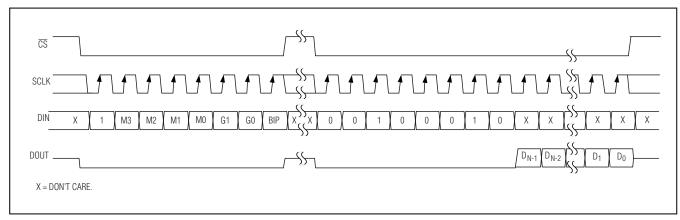

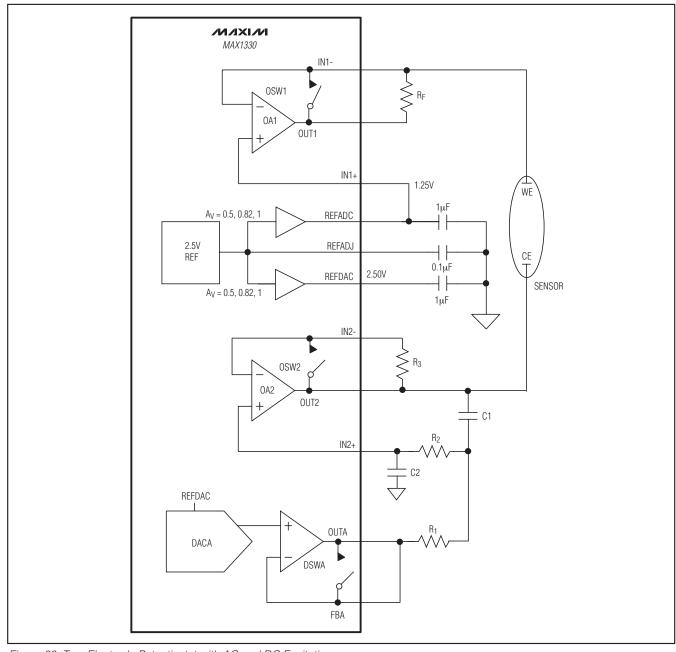

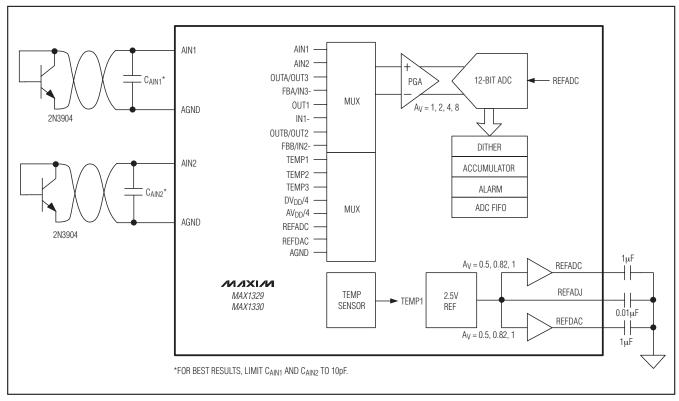

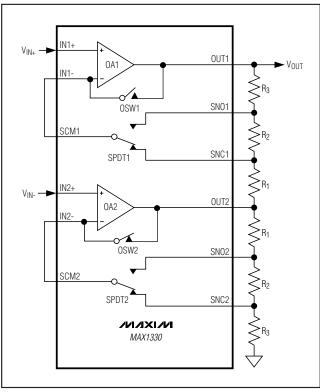

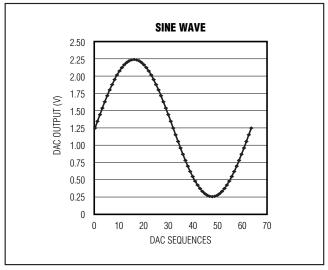

(AVDD = 5.0V, VREFADC = VREFDAC = 2.5V for DVDD = 3.0V; TA = +25°C, unless otherwise noted.)